## **LM390 1W Battery Operated Audio Power Amplifier**

## **General Description**

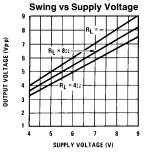

The LM390 Power Audio Amplifier is optimized for 6V, 7.5V, 9V operation into low impedance loads. The gain is internally set at 20 to keep the external part count low, but the addition of an external resistor and capacitor between pins 2 and 6 wil increase the gain to any value up to 200. The inputs are ground referenced while the output is automatically biased to one half the supply voltage.

### **Features**

- Battery operation

- 1W output power

- Minimum external parts

- Excellent supply rejection

- Ground referenced input

- Self-centering output quiescent voltage

- Variable voltage gain

- Low distortion

- Fourteen pin dual-in-line package

## **Applications**

- AM-FM radio amplifiers

- Portable tape player amplifiers

- Intercoms

- TV sound systems

- Lamp drivers

- Line drivers

- Ultrasonic drivers

- Small servo drivers

- Power converters

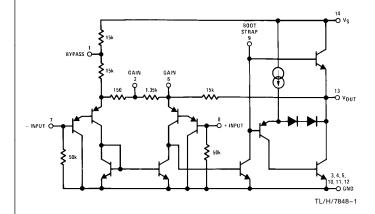

## **Equivalent Schematic and Connection Diagrams**

Order Number LM390N See NS Package Number N14A

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

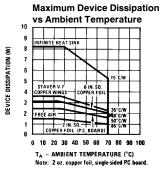

Supply Voltage 10V Package Dissipation 14-Pin DIP (Note 1) 8.3W Input Voltage  $\pm$  0.4V Storage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C

$\begin{array}{lll} \mbox{Operating Temperature} & \mbox{0°C to} + 70°\mbox{C} \\ \mbox{Junction Temperature} & 150°\mbox{C} \\ \mbox{Lead Temperature (Soldering, 10 sec.)} & 260°\mbox{C} \\ \mbox{Thermal Resistance} & & & \\ \mbox{$\theta_{\rm JC}$} & 30°\mbox{C/W} \\ \mbox{$\theta_{\rm JA}$} & 79°\mbox{C/W} \end{array}$

## **Electrical Characteristics** T<sub>A</sub> = 25°C, (Figure 1)

| Symbol            | Parameter                    | Conditions                                                                                                | Min | Тур      | Max | Units    |

|-------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|-----|----------|-----|----------|

| Vs                | Operating Supply Voltage     |                                                                                                           | 4   |          | 9   | V        |

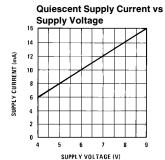

| IQ                | Quiescent Current            | $V_{S} = 6V, V_{IN} = 0$                                                                                  |     | 10       | 20  | mA       |

| Pout              | Output Power                 | $V_{	extsf{S}}=6	extsf{V}, 	extsf{R}_{	extsf{L}}=4\Omega, 	extsf{THD}=10\%$                               | 0.8 | 1.0      |     | W        |

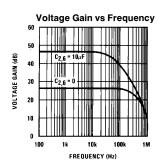

| A <sub>V</sub>    | Voltage Gain                 | $V_S = 6V$ , $f = 1$ kHz<br>10 $\mu$ F from Pin 2 to 6                                                    | 23  | 26<br>46 | 30  | dB<br>dB |

| BW                | Bandwidth                    | V <sub>S</sub> = 6V, Pins 2 and 6 Open                                                                    |     | 300      |     | kHz      |

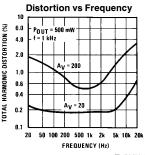

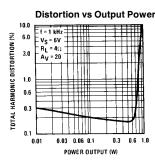

| THD               | Total Harmonic Distortion    | $V_S=6V, R_L=4\Omega, P_{OUT}=500 \text{ mW}$ f = 1 kHz, Pins 2 and 6 Open                                |     | 0.2      | 1   | %        |

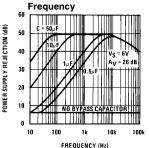

| PSRR              | Power Supply Rejection Ratio | $V_{\rm S}=$ 6V, f = 1 kHz, $C_{\rm BYPASS}=$ 10 $\mu F$ , Pins 2 and 6 Open, Referred to Output (Note 2) |     | 50       |     | dB       |

| R <sub>IN</sub>   | Input Resistance             |                                                                                                           | 10  | 50       |     | kΩ       |

| I <sub>BIAS</sub> | Input Bias Current           | V <sub>S</sub> = 6V, Pins 7 and 8 Open                                                                    |     | 250      |     | nA       |

Note 1: Pins 3, 4, 5, 10, 11, 12 at 25°C. Above 25°C case, derate at 15°C/W junction to case, or 85°C/W junction to ambient.

Note 2: If load and bypass capacitor are returned to V<sub>S</sub> (Figure 2), rather than ground (Figure 1), PSRR is typically 30 dB.

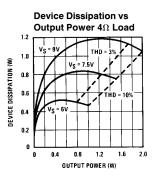

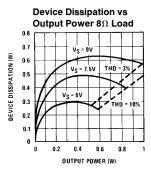

## **Typical Performance Characteristics**

Peak-to-Peak Output Voltage

# Power Supply Rejection Ratio (Referred to the Output) vs

TL/H/7848

## Typical Performance Characteristics (Continued)

TL/H/7848-6

### **Application Hints**

#### **Gain Control**

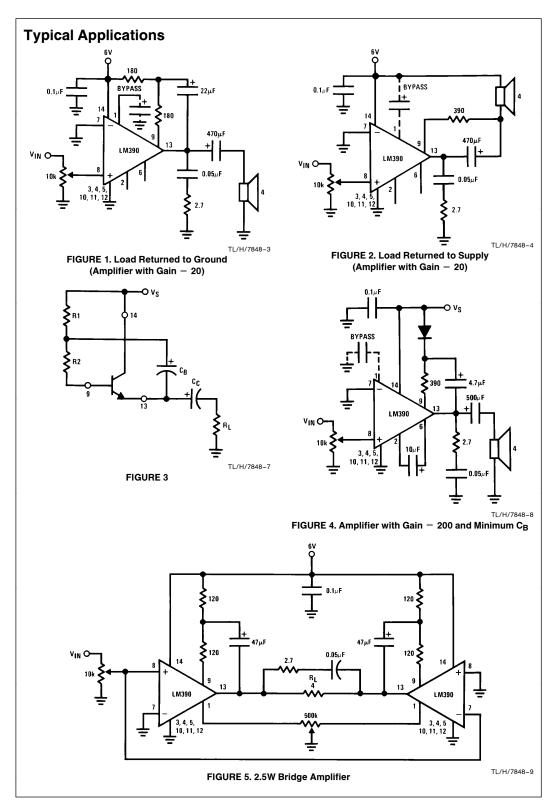

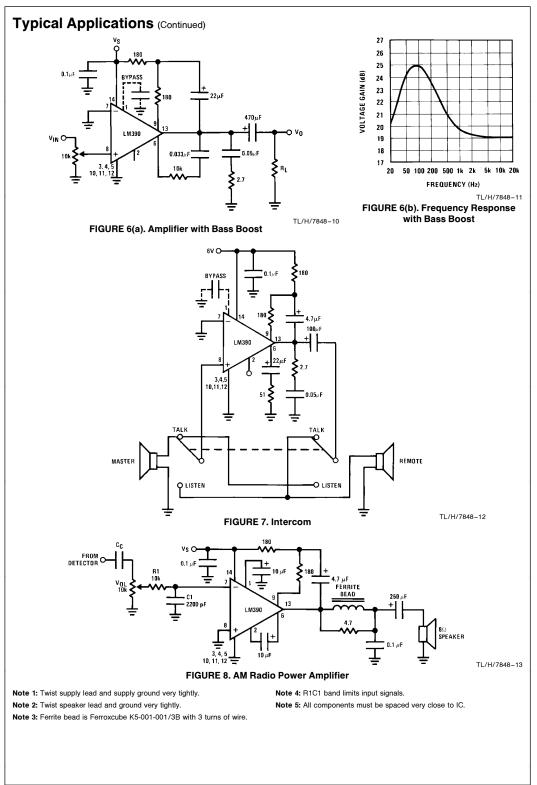

To make the LM390 a more versatile amplifier, two pins (2 and 6) are provided for gain control. With pins 2 and 6 open, the 1.35 k $\Omega$  resistor sets the gain at 20 (26 dB). If a capacitor is put from pin 2 to 6, bypassing the 1.35 k $\Omega$  resistor, the gain will go up to 200 (46 dB). If a resistor is placed in series with the capacitor, the gain can be set to any value from 20 to 200. A low frequency pole in the gain response is caused by the capacitor working against the external resistor in series with the 150 $\Omega$  internal resistor. If the capacitor is eliminated and a resistor connects pin 2 to 6 then the output dc level may shift due to the additional dc gain. Gain control can also be done by capacitively coupling a resistor (or FET) from pin 6 to ground, as in Figure 7.

Additional external components can be placed in parallel with the internal feedback resistors to tailor the gain and frequency response for individual applications. For example, we can compensate poor speaker bass response by frequency shaping the feedback path. This is done with a series RC from pin 6 to 13 (paralleling the internal 15  $k\Omega$  resistor). For 6 dB effective bass boost:  $R\cong 15~k\Omega$ , the lowest value for good stable operation is  $R=10~k\Omega$  if pin 2 is open. If pins 2 and 6 are bypassed then R as low as 2  $k\Omega$  can be used. This restriction is because the amplifier is only compensated for closed-loop gains greater than 9 V/V.

### **Input Biasing**

The schematic shows that both inputs are biased to ground with a 50  $k\Omega$  resistor. The base current of the input transistors is about 250 nA, so the inputs are at about 12.5 mV when left open. If the dc source resistance driving the LM390 is higher than 250  $k\Omega$  it will contribute very little additional offset (about 2.5 mV at the input, 50 mV at the output). If the dc source resistance is less than 10  $k\Omega$ , then shorting the unused input to ground will keep the offset low (about 2.5 mV at the input 50 mV at the output). For dc source resistances between these values we can eliminate excess offset by putting a resistor from the unused input to ground, equal in value to the dc source resistance. Of course all offset problems are eliminated if the input is capacitively coupled.

When using the LM390 with higher gains (bypassing the 1.35  $k\Omega$  resistor between pins 2 and 6) it is necessary to

bypass the unused input, preventing degradation of gain and possible instabilities. This is done with a 0.1  $\mu$ F capacitor or a short to ground depending on the dc source resistance on the driven input.

### **Bootstrapping**

The base of the output transistor of the LM390 is brought out to pin 9 for Bootstrapping. The output stage of the amplifier during positive swing is shown in *Figure 3* with its external circuitry.

R1  $\pm$  R2 set the amount of base current available to the output transistor. The maximum output current divided by beta is the value required for the current in R1 and R2:

$$(R1 + R2) = \beta_O \frac{(V_S/2) - V_{BE}}{I_{O,MAX}}$$

Good design values are  $V_{BE}=0.7V$  and  $\beta_O=100$ . Example 0.8 watt into  $4\Omega$  load with  $V_S=6V$ .

$$I_{O\;MAX} = \sqrt{\frac{2\,P_O}{R_L}} = 632\;\text{mA}$$

$$(R1\,+\,R2) = 100\left(\frac{(6/2)\,-\,0.7}{0.632}\right) = 364\Omega$$

To keep the current in R2 constant during positive swing capacitor  $C_B$  is added. As the output swings positive  $C_B$  lifts R1 and R2 above the supply, maintaining a constant voltage across R2. To minimize the value of  $C_B,\,R1=R2.$  The pole due to  $C_B$  and R1 and R2 is usually set equal to the pole due to the output coupling capacitor and the load. This gives:

$$C_{B} \cong \frac{4C_{C}}{\beta_{O}} \cong \frac{C_{C}}{25}$$

Example: for 100 Hz pole and R<sub>L</sub> =  $4\Omega$ ; C<sub>C</sub> =  $400~\mu\text{F}$  and C<sub>B</sub> =  $16~\mu\text{F}$ , if R1 is made a diode and R2 increased to give the same current, C<sub>B</sub> can be decreased by about a factor of 4. as in *Figure 4*.

For reduced component count the load can replace R1. The value of (R1 + R2) is the same, so R2 is increased. Now C<sub>B</sub> is both the coupling and the bootstrapping capacitor (see *Figure 2*).

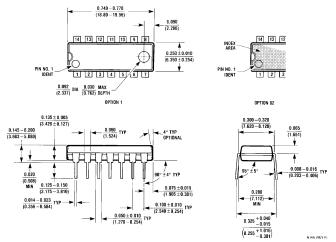

## Physical Dimensions inches (millimeters)

Molded Dual-In-Line Package (N) Order Number LM390N See NS Package Number N14A

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408 This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.